Table of contents

C-SOI wafers are a variant of SOI (Silicon-On-Insulator) wafers, where a cavity is intentionally created beneath the top silicon layer. This cavity can be designed to have specific dimensions and locations, providing unique electrical and thermal properties that can be leveraged in microelectromechanical systems (MEMS) and certain types of transistors.

Top Silicon Layer: This is the active silicon layer where devices are fabricated. The thickness of this layer is precisely controlled to ensure uniformity across the wafer.

Cavity Layer: Beneath the top silicon layer, a cavity or void is created. This cavity can vary in size and shape depending on the application. The cavity introduces air or vacuum spaces that can influence the mechanical and electrical characteristics of the wafer.

Buried Oxide (BOX) Layer: This insulating layer separates the top silicon layer from the bulk silicon substrate. It plays a crucial role in isolating the active devices from the substrate, reducing parasitic capacitance, and improving performance.

Handle Silicon (Substrate): The bottom layer is the bulk silicon, which provides mechanical support to the wafer.

MEMS Devices: C-SOI wafers are widely used in MEMS, where the cavities allow for the creation of movable parts like beams, mirrors, and sensors. The cavities provide the necessary space for these elements to operate.

RF and High-Speed Devices: The insulating properties of the SOI structure, combined with the cavity, reduce parasitic capacitance, making C-SOI wafers suitable for high-speed and radio frequency (RF) applications.

Thermal Management: The cavities can be used to enhance thermal insulation, which is critical in devices where thermal management is a concern.

Reduced Parasitic Capacitance: The insulating layers and cavities help minimize parasitic capacitance, leading to faster device operation and lower power consumption.

Improved Device Performance: The unique structure can enhance device performance, particularly in high-frequency and high-temperature applications.

Versatility in Design: The ability to customize the cavity size and shape provides flexibility in designing devices with specific characteristics.

The tables below give some guidelines on Xinekehui C-SOI wafer specifications. Our C-SOI wafers are always customized solutions, so please contact our sales and technical support for more detailed information.

| C-SOI wafer diameter | 150 mm, 200 mm |

| Device layer specifications | |

| Growth method | Cz, MCz, A-MCz |

| Crystal orientation | <100>, <110>, <111> |

| N type dopants | Antimony, Phosphorus |

| P type dopants | Boron |

| Resistivity | From <0.001 to >7,000 Ohm-cm* *Resistivity range varies by dopant and orientation |

| Device layer / membrane thickness | From 2 μm to >200 μm |

| Device layer / membrane thickness tolerance | Typically ±0.5 μm, down to ±0.2 μm with EC-SOI |

| Buried oxide (BOX) specifications | |

| Type | Thermal oxide grown on handle or device wafer or both |

| Thickness | From 0.3 μm to 4 μm, typically between 0.5 μm and 2 μm |

| Handle wafer specifications | |

| Growth method | Cz, MCz, A-MCz |

| Cz, MCz, A-MCz | <100>, <110>, <111> |

| N type dopants | Antimony, Phosphorus |

| P type dopants | Boron |

| Resistivity | From <0.001 to >7,000 Ohm-cm* *Resistivity range varies by dopant and orientation |

| Handle wafer thickness | 200 mm: 300 μm to 950 μm, typically 725 μm 150 mm: 300 μm to 950 μm, typically 380 μm |

| Handle wafer thickness tolerance | ±5 μm |

| Back surface | Polished or etched with oxide |

| Cavity specifications | |

| Cavity location | Handle wafer or device layer, or buried oxide |

| Cavity depth (in silicon) | 2 – 500 µm |

| Minimum CD | 2 µm |

| Max cavity span length vs. membrane thickness | <40:1 µm with standard C-SOI process |

| Front surface alignment marks | |

| Alignment accuracy, buried cavity to front surface alignment marks | ±1 µm |

| Mark design | Customer tool specific |

The processing technology of C-SOI (Cavity Silicon on Insulator) wafers is a specialized fabrication technique used in the semiconductor industry, primarily for producing advanced microelectronic devices. C-SOI wafers are used in applications where high performance, low power consumption, and enhanced device characteristics are critical, such as in RF (Radio Frequency) applications, MEMS (Micro-Electro-Mechanical Systems), and advanced CMOS (Complementary Metal-Oxide-Semiconductor) technology.

1. Base SOI Wafer Fabrication

The process begins with the fabrication of an SOI (Silicon on Insulator) wafer. This typically involves the use of either the Smart Cut™ technology or the SIMOX (Separation by IMplantation of OXygen) process. The SOI wafer consists of a thin silicon layer (device layer) on top of a buried oxide (BOX) layer, which in turn is on a silicon substrate.

2. Cavity Formation

The key feature of C-SOI wafers is the creation of cavities within the silicon layer. These cavities are formed beneath the device layer and within the buried oxide layer.

The cavity formation can be achieved through various techniques, such as wet or dry etching. The process is carefully controlled to create cavities of precise dimensions, which are critical for the intended device performance.

Anisotropic etching is commonly used to create well-defined cavities with specific shapes and sizes.

3. Thin Film Deposition

After the cavities are formed, a thin silicon film is deposited over the cavity region. This step is crucial as it seals the cavities and forms the final device layer.

The deposition method used may include techniques like Chemical Vapor Deposition (CVD), where a thin and uniform silicon layer is deposited over the entire wafer.

4. Bonding and Layer Transfer

In some cases, a bonding process is employed to transfer the cavity-containing layer onto another substrate. This is achieved through wafer bonding, where the cavity structure is bonded to a handle wafer, and the original wafer is then removed or thinned.

The bonding process needs to ensure a high degree of alignment and low defectivity to maintain the integrity of the cavities and overall wafer quality.

5. Polishing and Thinning

The top silicon layer (device layer) is often polished and thinned to the required thickness. This is typically achieved using CMP (Chemical Mechanical Polishing) to obtain a smooth, defect-free surface suitable for device fabrication.

6. Device Fabrication

Once the C-SOI wafer is prepared, standard semiconductor processing techniques, including lithography, etching, doping, and metallization, are used to fabricate the desired electronic or MEMS devices on the wafer.

7. Quality Control and Testing

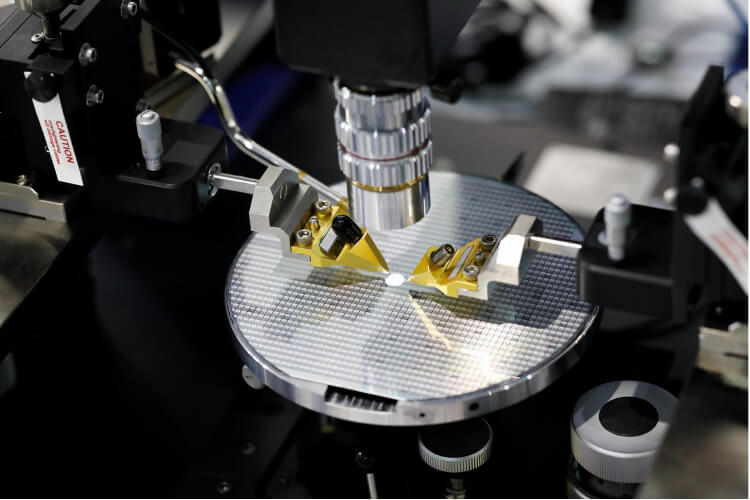

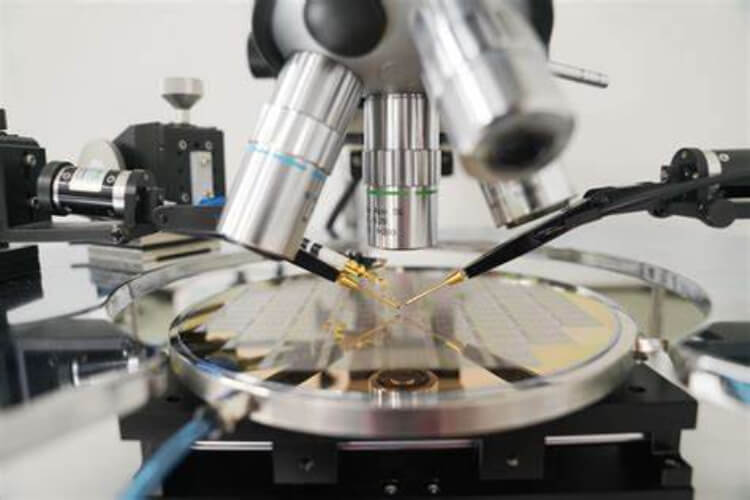

Throughout the processing stages, rigorous quality control measures are implemented to ensure the wafer meets the required specifications. This includes inspections for defects, measurements of the cavity dimensions, and electrical testing of the wafer.

In terms of processing C-SOI (Complimentary-Silicon-On-Insulator) Wafers, Xinkehui has the following advantages:

1. Material cost and supply chain optimization

(1) Efficient use of raw materials: The use of SOI technology can reduce the waste of silicon materials because it only uses high-purity silicon in key areas, reducing the overall material cost.

(2) Stable supply chain: By optimizing material procurement and supply chain management, a stable supply of raw materials can be ensured and the risk of fluctuations can be reduced.

2. Technical precision and process control

(1) Extremely high process control: In the manufacture of C-SOI Wafer, precise control of parameters such as thickness and flatness is crucial. High-precision processing technology can ensure that these parameters meet strict specifications, thereby improving product quality and consistency.

(2) Reducing wafer defects: Through advanced manufacturing processes, micro defects on wafers can be effectively reduced and the yield rate can be improved.

3. Performance advantages

(1) Reduce power consumption and improve performance: C-SOI Wafer performs well in circuits, especially in high-frequency applications, and can significantly reduce power consumption and increase speed, which is critical for mobile devices and high-performance computing.

(2) Improve thermal management capabilities: The insulating layer of the SOI structure can effectively reduce parasitic capacitance, reduce leakage current, and improve thermal management capabilities.

4. Process flexibility and compatibility

(1) Compatible with multiple manufacturing processes: C-SOI Wafers are compatible with a variety of semiconductor manufacturing processes, including CMOS processes. This makes them easier to integrate on existing production lines, reducing the need for equipment adjustments and process improvements.

(2) Flexible design space: C-SOI technology allows designers to have greater flexibility in device layout and structure, enabling the design of more compact and efficient integrated circuits.

5. Market and application advantages

(1) Meeting high-demand markets: With the rapid development of emerging technologies such as 5G, artificial intelligence, and the Internet of Things, the demand for C-SOI Wafers is also growing. Advanced manufacturing capabilities enable companies to respond quickly to market demand and seize more business opportunities.

(2) Wide range of applications: C-SOI Wafers are widely used in mobile communications, automotive electronics, high-performance computing and other fields, and have strong market competitiveness.

In addition to C-SOI Wafers , we can also provide you with many other optical products. We look forward to your consultation.